래치(Latch)

래치는 순차회로에서 한 비트의 정보를 저장하는 회로이다. 인에이블(허용)이 되면 레벨을 감지하여 입력값을 출력으로 계속해서 전송한다.

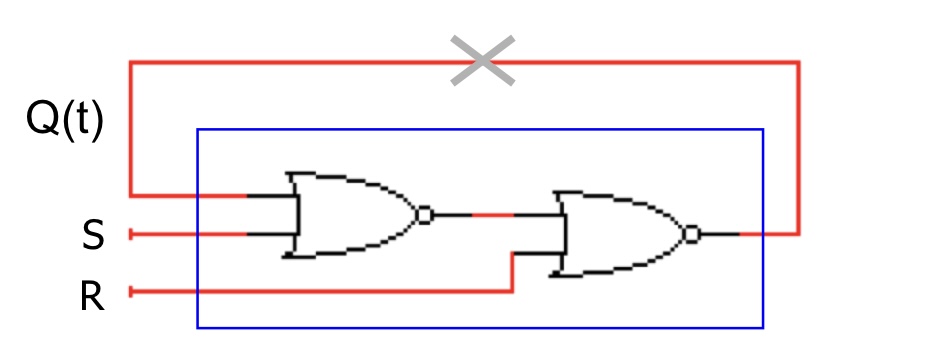

NOR형 SR래치

S는 Set, R은 Reset을 의미하며, 두 개의 입력에 따라 두 개의 출력을 가진다.

<NOR형 SR래치 진리표>

| S | R | Q | Q' |

| 0 | 0 | q | q |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | X | X |

여기서 q란 과거의 값을 의미한다. 즉, S와 R이 0이면 과거의 값이 보존된다.

+ 래치는 Enable에 의해 회로가 동작하는 반면, 플립플롭은 CLK에 의해 회로가 동작한다.

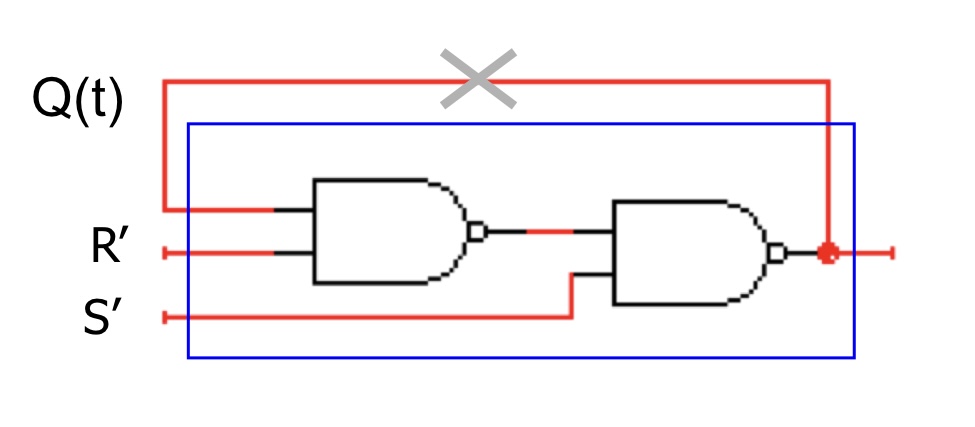

NAND형 SR래치

NAND형 SR래치에서 주의해야 할 점은 입력으로 inverting된 값이 들어간다는 것이다.

<NAND형 SR래치 진리표>

| S | R | Q | Q' |

| 0 | 0 | X | X |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | q | q |

SR latch using NOR gates with cut feedback loop

<SR래치 진리표>

| S | R | Q(t) | Q(t+△) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | X |

| 1 | 1 | 1 | X |

Q(t+△) = S + R' Q(t) 성립

SR latch using NAND gates with cut feedback loop

<SR래치 진리표>

| S | R | S' | R' | Q(t) | Q(t+△) |

| 0 | 0 | 1 | 1 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 0 | X |

| 1 | 1 | 0 | 0 | 1 | X |

Q(t+△) = S + R'Q(t) 성립

+ 래치 -> level sensitive

+ 플립플롭 -> edge triggered

Enable형 RS 래치

기본래치의 입력단에 각각의 AND 회로가 있어 AND 회로의 출력이 래치에 입력된다.

EN = 0이면 S와 R에 관계없이 S'와 R'는 모두 0이다.

EN = 1이면 S' = S 및 R' = R이 되어 기본 래치로 동작한다.

(즉, Enable 신호에 따라 래치의 동작을 제어한다.)

위 회로도의 경우, EN = 0일 때 input값이 의미가 있어진다.

'2-1 학기 > Logic Circuit' 카테고리의 다른 글

| [논리회로] 카운터(Counter) (0) | 2023.05.28 |

|---|---|

| [논리회로] 플립플롭(Flip-Flop) (1) | 2023.05.28 |